News

NXP’s Edge LLM Strategy: Kinara, RAG, Agents

NXP has unveiled its strategy for enabling large language model (LLM) inference on edge devices at the Embedded Vision Summit 2025. The company announced the acquisition of AI accelerator startup Kinara, whose Ara-2 chip enhances LLM performance. With the introduction of GenAI Flow, NXP aims to optimize edge applications by integrating RAG techniques to provide contextual awareness to LLMs, crucial for sectors like automotive and healthcare.

Launches

News Highlights from Embedded Vision Summit 2025

The Embedded Vision Summit showcased numerous advancements in edge AI technologies. MemryX was awarded for its MX3 M.2 AI accelerator module, which combines ease of use with efficient performance. Nota AI demonstrated its collaboration with Qualcomm, revealing its enhanced AI model optimization platform. SiMa.ai and Wind River introduced a powerful integrated edge AI solution, while Vision Components presented a modular MIPI bricks system for embedded vision applications.

Charts

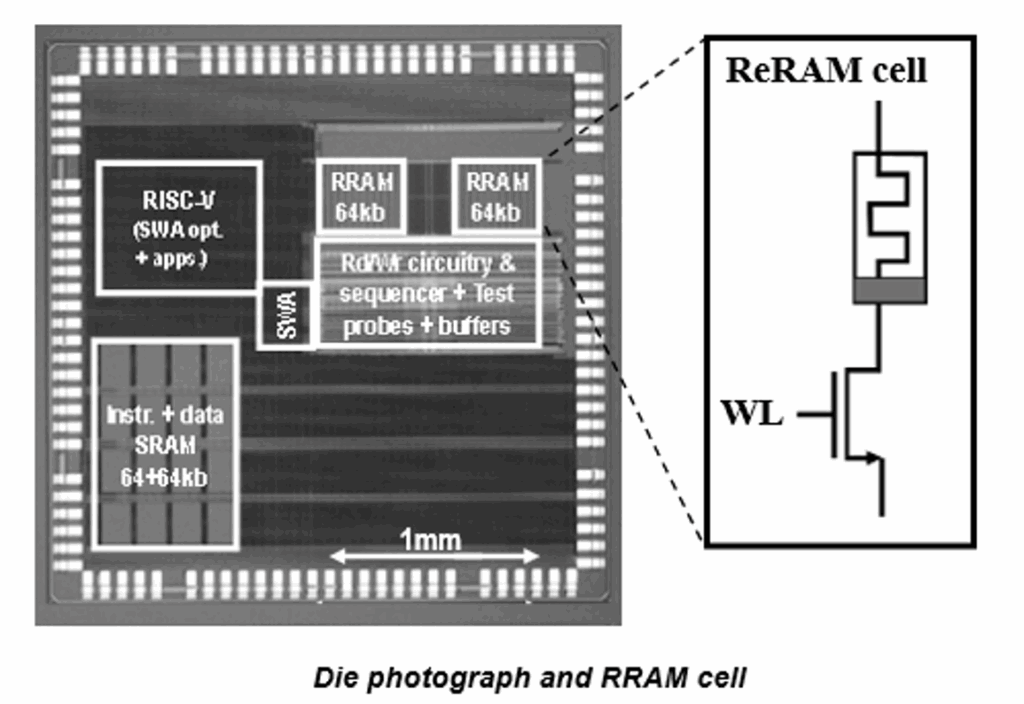

Aware Programming in ReRAM: Evaluating and Optimizing Write Termination

The research highlights the advancements in Resistive RAM (ReRAM) technology, particularly in managing conductance drift through voltage overdrive techniques. This method stabilizes memory performance while maintaining energy efficiency, showcasing potential improvements in neuromorphic computing applications. The findings illustrate the balance between energy consumption and stability, crucial for future memory technologies.

Research

Roadmap for AI HW Development, With The Role of Photonic Chips In Supporting Future LLMs

A collaborative research paper explores the future of AI computing hardware, emphasizing the role of photonic chips in supporting next-generation large language models (LLMs). The paper outlines the need for innovative computing paradigms, including integrated photonic neural networks and neuromorphic devices, to meet the growing demands of AI models, which are projected to require significant power resources.

Insight

Breker Verification Systems at the 2025 Design Automation Conference

Breker Verification Systems showcased its Synthesis and SystemVIP library at DAC 2025, emphasizing the need for advanced verification methodologies in semiconductor design. The solutions presented focus on enhancing verification coverage for complex applications, including AI accelerators and RISC-V cores. Breker’s AI-driven test suite synthesis aims to streamline the testing process, crucial for developing robust semiconductor solutions.

Stay tuned for more updates and insights from the semiconductor industry as we continue to track innovations and advancements shaping the future of technology.