News

Tag-Based Memory Verification System for RISC-V

Researchers from Inha University and Intel Labs have introduced a novel tag-based memory verification system tailored for embedded RISC-V processors. This system significantly enhances memory safety by integrating hardware-level mechanisms that detect heap-related vulnerabilities. The implementation shows promising performance improvements while maintaining low overhead, marking a substantial step forward in securing embedded systems.

Launches

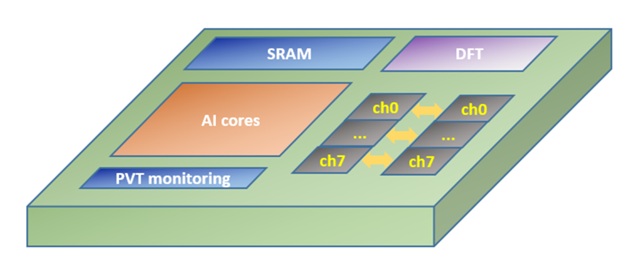

Alchip Launches 2nm Design Platform for HPC and AI ASICs

Alchip Technologies has launched its groundbreaking 2nm Design Platform, aimed at enhancing custom silicon design for high-performance computing and AI applications. This platform supports advanced chiplet integration strategies, allowing seamless combination of different node technologies to optimize performance and design flexibility, positioning Alchip at the forefront of TSMC’s next-generation semiconductor technologies.

Charts

DL Compiler Framework For More Efficient Inter-Core Connected AI Chips

The University of Illinois Urbana-Champaign and Microsoft have unveiled the Elk compiler framework, which optimizes inter-core connected AI chips. The framework systematically balances compute, communication, and I/O tasks, achieving impressive performance metrics. This is a crucial advance in maximizing the efficiency of AI chips in handling large models, illustrated with performance comparison charts and efficiency metrics.

Research

Siemens Proposes Unified Static and Formal Verification with AI

Siemens has introduced a novel approach to verification by combining static and formal methods with AI. This new offering, Questa One SFV, aims to simplify license management while enhancing the accuracy of verification processes. The research highlights how AI can improve the efficacy of traditional verification methods, paving the way for broader applications in semiconductor design.

Insight

Executive Interview with Shelly Henry of MooresLabAI

In an insightful interview, Shelly Henry, CEO of MooresLabAI, discusses the transformative potential of AI in semiconductor development. The VerifAgent™ AI platform promises to accelerate verification processes significantly, addressing the industry’s talent shortage while reducing costs. Henry emphasizes the importance of tailored AI solutions in enhancing semiconductor design efficiency.

Stay tuned for more cutting-edge updates and insights from the semiconductor world as we continue to track innovations that shape our industry!