News

Noise Margin Enhancing ULVR SRAM Cell

Researchers at the Tokyo Institute of Technology have published a new technical paper on a novel ultralow-voltage retention (ULVR) SRAM cell. This design significantly enhances noise immunity at ultralow voltages, demonstrating superior performance over conventional cells. The proposed 8T cell design can reduce standby power by approximately 93% compared to traditional 6T-SRAM macros, ensuring robustness in various operating modes.

Launches

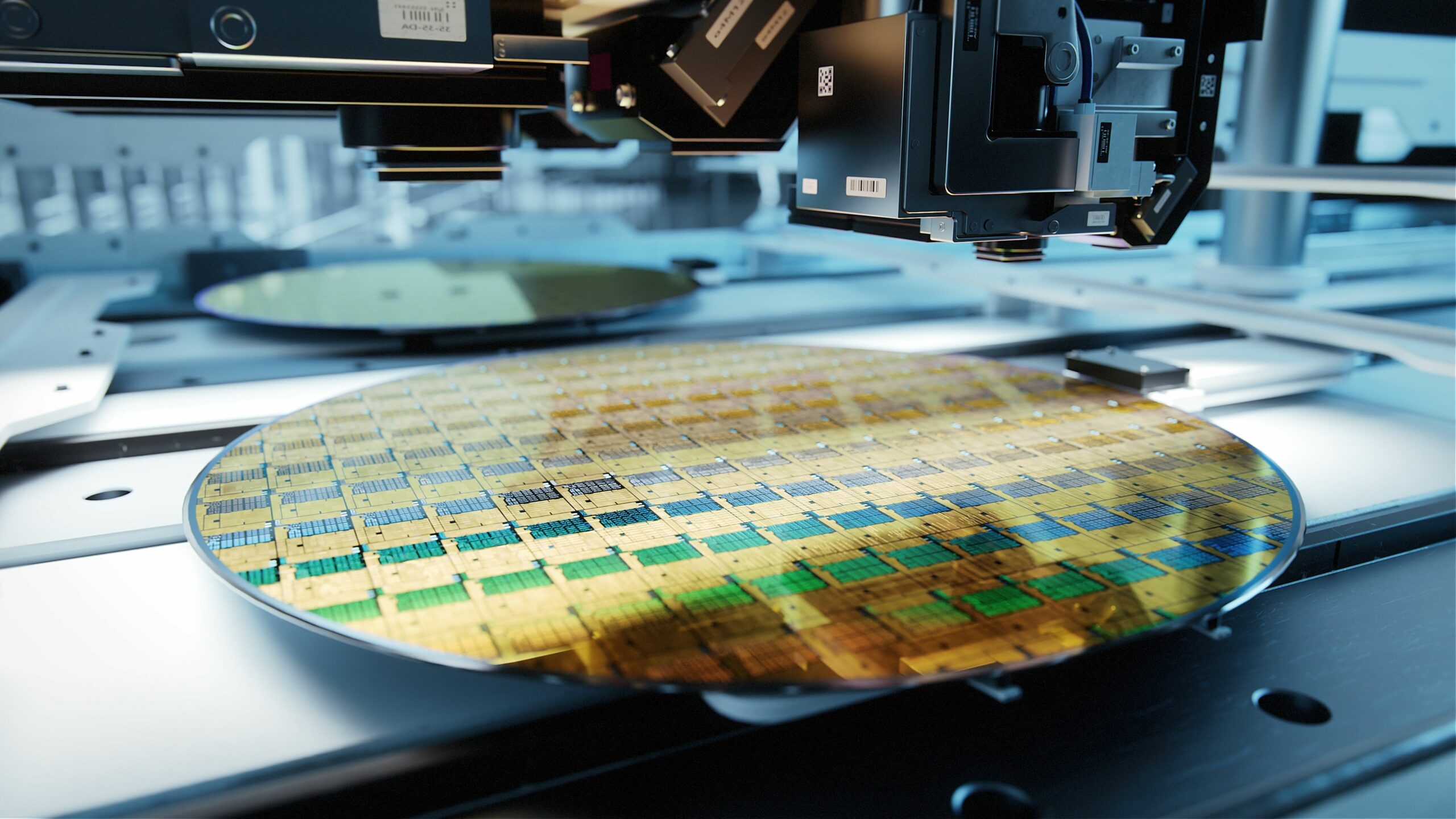

Epitaxial Growth Of Up To 120 Si/SiGe Bilayers

Imec and Ghent University have reported on the successful epitaxial growth of Si/SiGe multi-stacks aimed at 3D DRAM applications. Their research focuses on overcoming challenges in layer thickness and interface sharpness, crucial for efficient 3D dynamic random access memory devices. The work demonstrates the potential for high etching selectivity and manageable misfit dislocations, paving the way for advanced memory technologies.

Charts

LLM Inference: Core Bottlenecks Imposed By Memory, Compute Capacity

NVIDIA has released a detailed analysis of the performance bottlenecks encountered in large language model (LLM) inference. Their research highlights the critical role of memory bandwidth and synchronization latencies in maximizing throughput. Key findings indicate that high memory bandwidth and reduced synchronization latencies are essential for effective LLM deployment, providing a framework for future hardware advancements.

Research

Agentic AI and the EDA Revolution

The emergence of Agentic AI is revolutionizing the EDA and semiconductor industries by addressing chip design complexities and a shortage of skilled engineers. As highlighted in recent discussions at industry events, effective data mobility, security, and availability are vital for leveraging Agentic AI’s potential, enabling smarter automation in semiconductor design processes.

Insight

DAC TechTalk – A Siemens and NVIDIA Perspective

At the recent DAC event, Siemens and NVIDIA discussed the transformative impact of AI on semiconductor design. Emphasizing the necessity for AI in overcoming design complexity and time-to-market challenges, the presentation outlined how their collaboration is set to enhance design quality and productivity, showcasing real-world results and future directions for AI in EDA.

Stay tuned for more updates and insights into the ever-evolving semiconductor landscape!