News

What It Really Takes to Build a Future-Proof AI Architecture

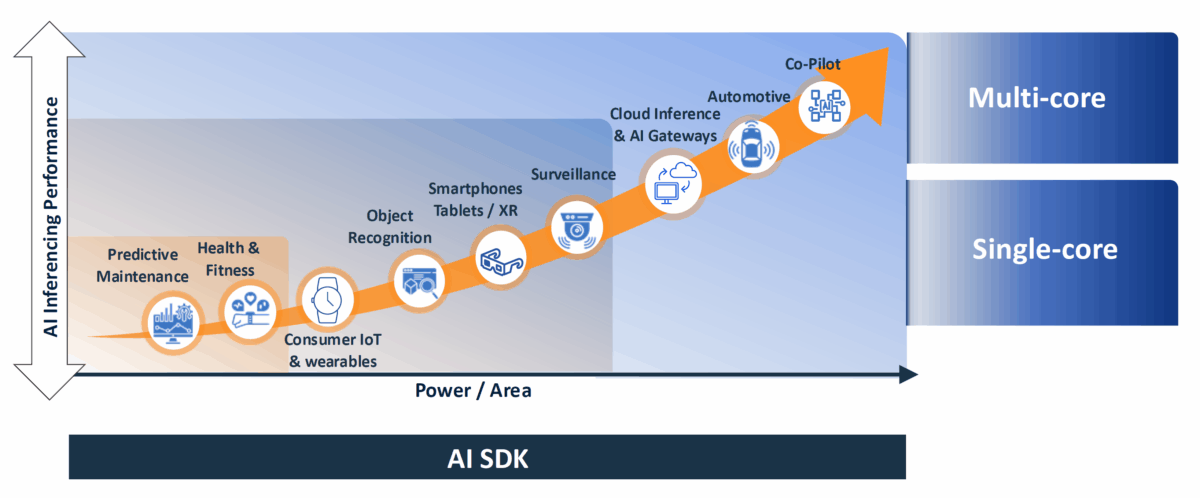

Ceva hosted a webinar discussing the necessity of specialized AI inference chips for edge devices, addressing how these chips can meet specific embedded requirements while maintaining energy efficiency. The discussion emphasized the importance of designing flexible architectures that can adapt to rapid advancements in AI technology.

Launches

Architecting Your Next SoC: Join the Live Discussion on Tradeoffs…

A live webinar was held to explore the complexities involved in designing a system-on-chip (SoC). Experts discussed the trade-offs in architecture, IP selection, and ecosystem realities, aiming to equip attendees with actionable strategies for navigating the challenges in SoC design.

Charts

LtRAM And StRAM: Specialized Memory Architectures

A new paper from Stanford and Microsoft presents a proposal for specialized memory architectures: Long-term RAM (LtRAM) and Short-term RAM (StRAM). The authors argue that such architectures can optimize performance based on specific application access patterns, addressing the limitations of traditional memory hierarchies.

Research

In-NAND Self-Encryption Architecture In A 4D-NAND Structure

The researchers from DGIST and Georgia Tech introduce FlashVault, an innovative architecture that embeds a cryptographic engine within NAND flash chips. This design allows for enhanced data security at zero area overhead, significantly improving performance for various cryptographic algorithms.

Insight

A Quick Tour Through Prompt Engineering as it Might Apply to Debug

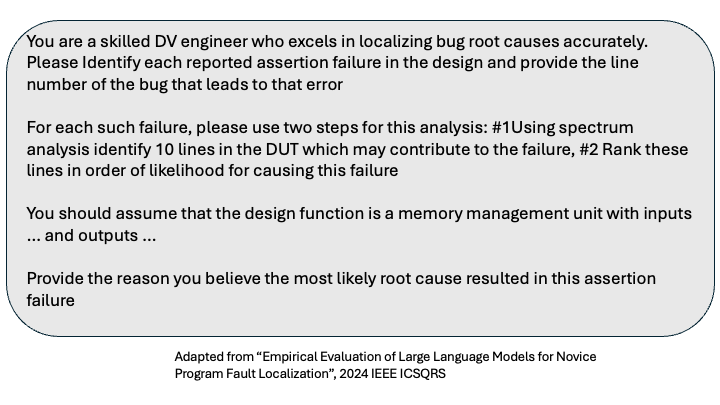

This article explores the emerging discipline of prompt engineering, particularly its importance in optimizing large language model (LLM) interactions for hardware debugging. With techniques like Chain of Thought prompting and in-context learning, the article emphasizes the need for engineers to adapt their approach to leverage LLMs effectively in debugging processes.

Stay tuned for more insights and developments in the semiconductor industry as we continue to bring you the latest news and innovations!