News

Cost-Effective, Orthogonal Approach to Resilient Memory Design

A new paper from researchers at the University of Central Florida, UT San Antonio, and Rochester introduces SCREME, a scalable framework for resilient memory design. This approach challenges traditional Error Correction Codes (ECC) by proposing the use of cost-effective, lower-performance chips, which can help meet the growing demands for reliability in memory technology. The insights aim to optimize memory space utilization and enhance performance.

Launches

KAN Acceleration: Algorithm Hardware Co-Design Approach

Researchers from Georgia Tech, National Tsing Hua University, and TSMC have unveiled a new algorithm-hardware co-design framework for optimizing Kolmogorov-Arnold Networks (KAN). This innovative architecture enhances deep neural network capabilities while minimizing the need for extensive hardware resources. The paper details circuit-level optimizations that improve performance and reduce power consumption significantly, paving the way for large-scale KAN implementations.

Charts

HW-SW Co-Designed System With 3 Core Optimization Pathways For Long-Context Agentic LLM Inference

A new study from Cambridge and Imperial College London presents PLENA, a system designed to optimize long-context LLM inference. The research showcases a significant increase in hardware utilization and throughput when compared to existing accelerators, demonstrating the impact of innovative hardware-software co-design strategies on efficiency in AI applications.

Research

Analog Plus 3D Optics to Accelerate AI Inference and Combinatorial Optimization

Microsoft Research has published findings on an analog optical computer that integrates analog electronics with 3D optics for enhanced AI inference and optimization tasks. This innovative approach avoids traditional digital conversions, significantly improving energy efficiency. The research highlights case studies that demonstrate the potential of this technology to tackle complex AI and optimization challenges more sustainably.

Insight

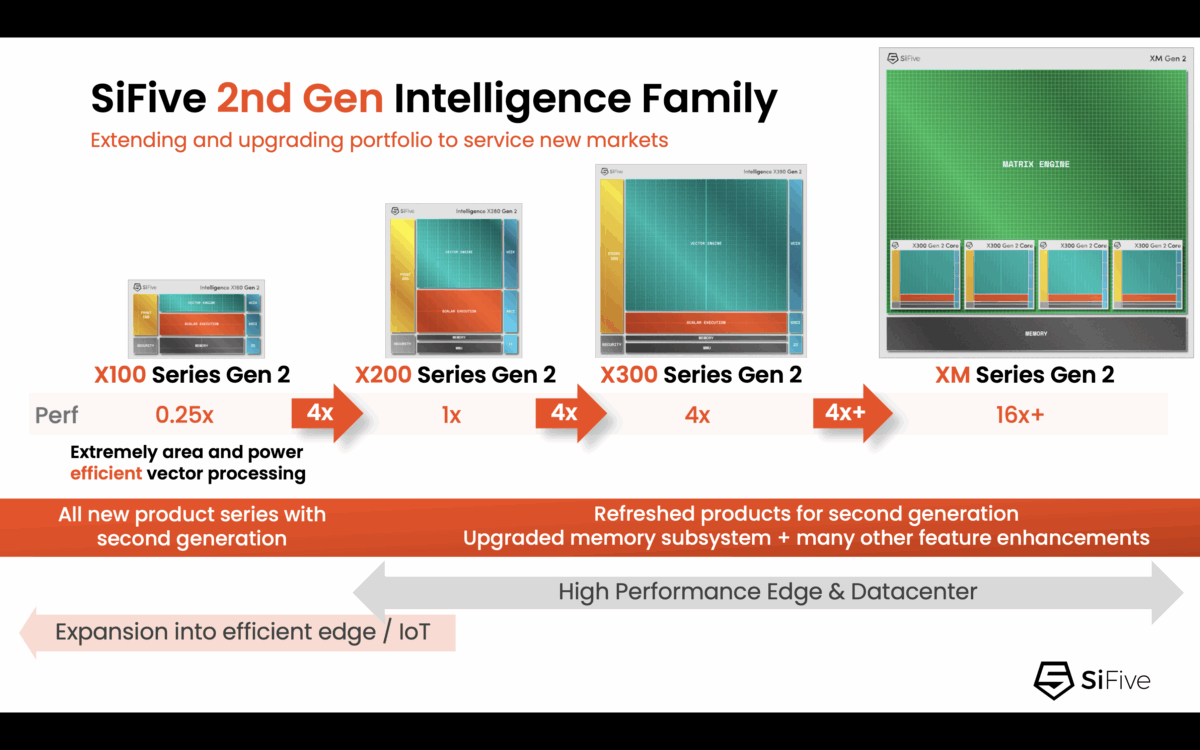

Generation Intelligence Family of RISC-V Cores Launched by SiFive

SiFive’s launch of its second-generation Intelligence Family of RISC-V processor IP cores marks a significant advancement in AI processing. The new X100 series promises to outperform current competitors while focusing on low power requirements. The leadership team discusses the implications of these innovations for AI-driven compute, solidifying RISC-V’s position as a strong alternative in the semiconductor landscape.

Stay tuned for more updates and breakthroughs in the semiconductor industry as we continue to bring you the latest news and insights!