News

Double Duty Logic Block Architecture Enabling Concurrent LUT and Adder Chain Usage

A recent paper by researchers at Nanyang Technological University and partners introduces the Double Duty logic block architecture, allowing for concurrent usage of look-up tables (LUTs) and adder chains in FPGAs. This approach enhances arithmetic density and reduces area by up to 21.6% in adder-intensive circuits, while maintaining critical path delay.

Launches

The path to smaller denser and faster

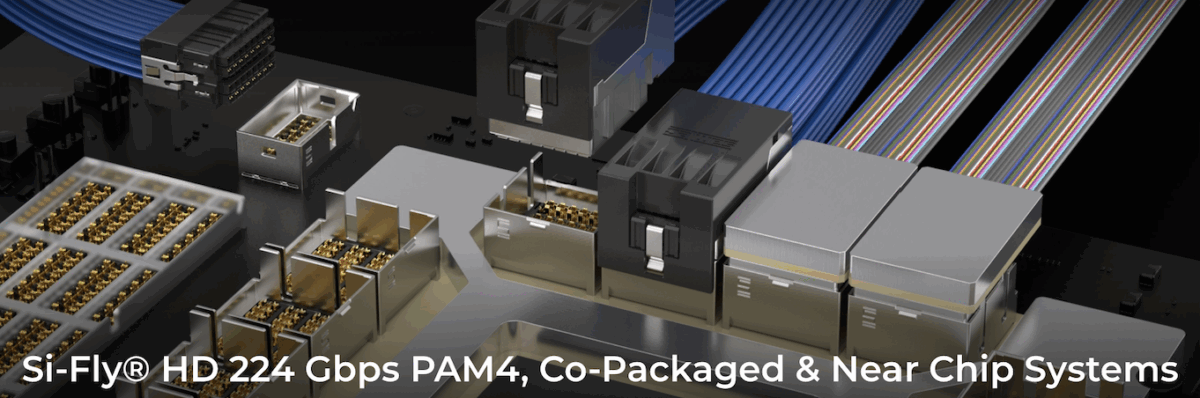

Samtec is set to host a webinar on October 21, discussing its innovative co-packaged copper (CPC) and co-packaged optics (CPO) technology, termed CPX. This development allows for advanced speeds of 224 Gbps, effectively integrating copper and optics for improved performance in data centers and AI applications.

Charts

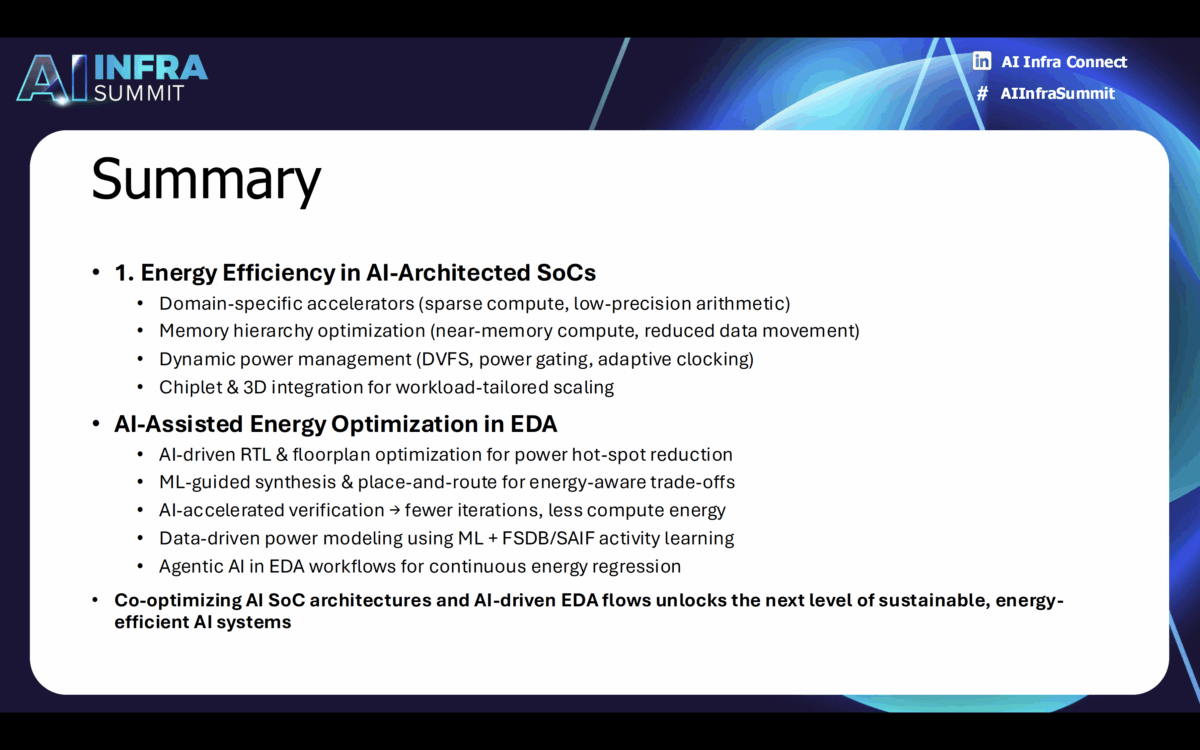

AI Everywhere in the Chip Lifecycle: Synopsys at AI Infra Summit

At the AI Infra Summit, Synopsys illustrated how AI influences every phase of chip development, reducing design times by up to 40% and improving energy efficiency due to the expected fifty-fold growth in AI workloads by 2028. Their unified AI-driven ecosystem integrates design and verification, streamlining the semiconductor development process.

Research

Neurosymbolic code generation. Innovation in Verification

A novel research paper from Rice University and collaborators proposes a neurosymbolic approach to automated code generation, significantly enhancing the accuracy of Java method generation. The method integrates symbolic reasoning with neural networks, achieving an impressive 86% success rate in syntax correctness checks compared to traditional large language models.

Insight

CEO Interview with Howard Pakosh of TekStart

Howard Pakosh, CEO of TekStart, discusses the evolution of his company into a venture builder focused on semiconductors and AI. He highlights the challenges of supply chain fragility and energy efficiency while showcasing their Newport initiative, which delivers performance-per-watt advancements for Edge AI applications, addressing critical needs in various sectors.

Stay tuned for more updates as we continue to bring you the latest in semiconductor and AI technology advancements.