News

IC and Silicon Labs Raise the Bar for Hardware Security

Cybersecurity is becoming increasingly critical as AI-driven attacks escalate, necessitating enhanced hardware security measures. Secure-IC’s Securyzr™ neo Core Platform has been integrated into Silicon Labs’ SiXG301 SoC, establishing a Root of Trust that offers advanced protection against sophisticated threats. This collaboration has achieved the first-ever PSA Level 4 certification, providing robust assurance against physical and cyber attacks in connected devices.

![]()

Launches

On-Package Memory With UCIe To Improve Bandwidth Density And Power Efficiency

Researchers at AMD and Intel have introduced a novel approach to on-package memory that leverages Universal Chiplet Interconnect Express (UCIe) technology. This development aims to enhance bandwidth density by up to 10x and reduce power consumption by up to 3x, addressing the growing demand for efficient memory solutions in AI and high-performance computing applications.

Charts

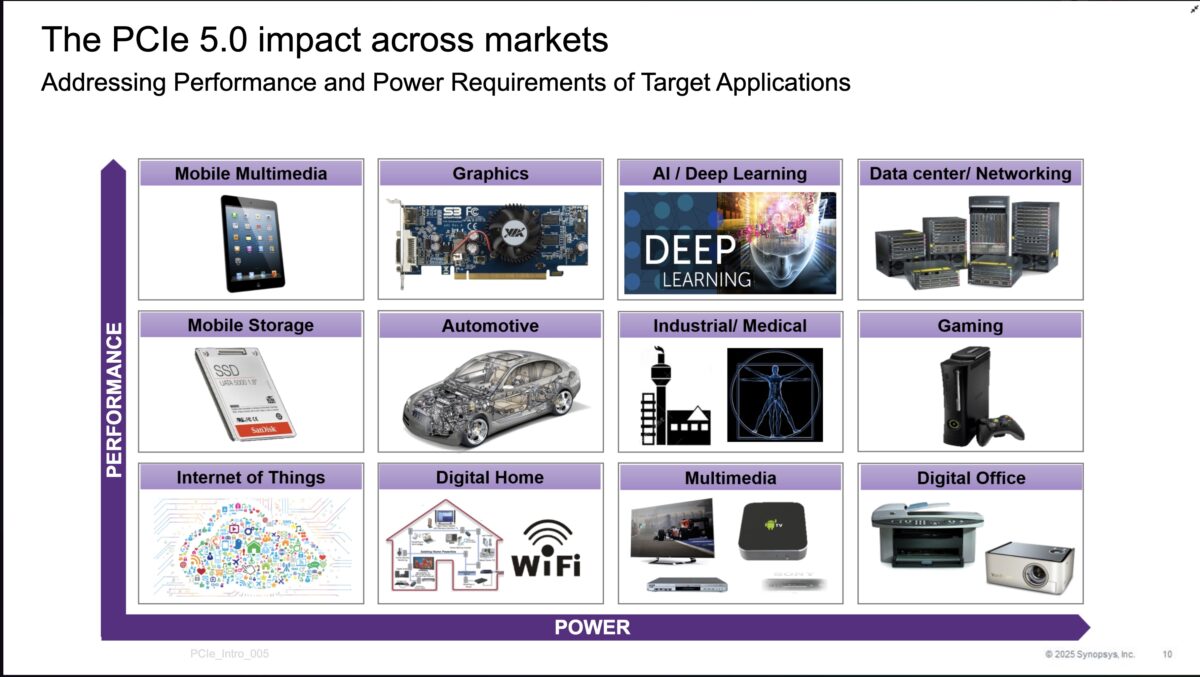

Why Choose PCIe 5.0 for Power, Performance and Bandwidth at the Edge

The latest webinar by Synopsys highlights the continued relevance of PCIe 5.0 in the era of Edge AI and high-performance applications. The chart showcases how PCIe 5.0 delivers high bandwidth and low latency, making it an ideal choice for a variety of sectors including automotive and data centers, while supporting the exponential growth of AI workloads.

Research

System-HW Co-Design Approach Combines Mono3D DRAM, NMP, and GPU Acceleration

A groundbreaking paper from researchers at UCSD and other institutions introduces “Stratum,” a co-design framework that integrates Mono3D DRAM with near-memory processing and GPU acceleration. This novel approach significantly improves decoding throughput by 8.29x and energy efficiency by 7.66x, offering a promising solution for deploying large-scale language models effectively.

Insight

Heterogeneous System With Specialized HW For Disaggregated LLM Inference

A panel discussion featuring experts from Princeton University and University of Washington unveiled insights into their latest research on specialized hardware for disaggregated LLM inference. The proposed SPAD architecture optimizes performance and cost, achieving significant hardware savings while meeting the demands of modern AI applications. This approach emphasizes the importance of tailored hardware solutions in the evolving landscape of machine learning.

Stay connected with us for the latest updates in the semiconductor industry as we continue to explore innovations and trends shaping the future.